# Over 100x Faster Bootstrapping in Fully Homomorphic Encryption through Memory-centric Optimization with GPUs

Wonkyung Jung<sup>1</sup>, Sangpyo Kim<sup>1</sup>, Jung Ho Ahn<sup>1</sup>, Jung Hee Cheon<sup>1,2</sup> and Younho Lee<sup>3</sup>

<sup>1</sup> Seoul National University, Seoul, Republic of Korea, {jungwk,vnb987,gajh,jhcheon}@snu.ac.kr <sup>2</sup> Crypto Lab. Inc, Seoul, South Korea, <sup>3</sup> SeoulTech, Seoul, Republic of Korea, younholee@seoultech.ac.kr

**Abstract.** Fully Homomorphic encryption (FHE) has been gaining in popularity as an emerging means of enabling an unlimited number of operations in an encrypted message without decryption. A major drawback of FHE is its high computational cost. Specifically, a *bootstrapping* step that refreshes the noise accumulated through consequent FHE operations on the ciphertext can even take minutes of time. This significantly limits the practical use of FHE in numerous real applications.

By exploiting the massive parallelism available in FHE, we demonstrate the first instance of the implementation of a GPU for bootstrapping CKKS, one of the most promising FHE schemes supporting the arithmetic of approximate numbers. Through analyzing CKKS operations, we discover that the major performance bottleneck is their high main-memory bandwidth requirement, which is exacerbated by leveraging existing optimizations targeted to reduce the required computation. These observations motivate us to utilize memory-centric optimizations such as kernel fusion and reordering primary functions extensively.

Our GPU implementation shows a 7.02× speedup for a single CKKS multiplication compared to the state-of-the-art GPU implementation and an amortized bootstrapping time of 0.423us per bit, which corresponds to a speedup of 257× over a single-threaded CPU implementation. By applying this to logistic regression model training, we achieved a  $40.0\times$  speedup compared to the previous 8-thread CPU implementation with the same data.

**Keywords:** Fully Homomorphic Encryption  $\cdot$  Bootstrapping  $\cdot$  Logistic regression  $\cdot$  GPU  $\cdot$  Kernel fusion

#### 1 Introduction

Homomorphic encryption (HE) enables one to perform operations on encrypted data without decrypting them and the result can be decrypted only with the secret key. As HE reveals nothing about the input or output except for the corresponding sizes during the computation step, it has been spotlighted as a core technology for applications such as privacy-preserving computations. HE schemes in the early stages had restrictions on the number and type of operations. After Gentry's breakthrough, however, these restrictions were removed, leading to Fully Homomorphic Encryption (FHE), where unlimited operations are allowed with the help of a bootstrapping operation [Gen09].

CKKS (Cheon-Kim-Kim-Song), an FHE scheme based on the ring learning with errors (RLWE) problem, is also a method that has recently attracted attention given its

Licensed under Creative Commons License CC-BY 4.0.

Received: 2021-04-15 Accepted: 2021-06-15 Published: 2021-08-11

efficient approximate computation [CHK<sup>+</sup>19]. As opposed to other FHE schemes, this scheme is equipped with rounding operations as well as the addition and multiplication of real numbers as primitive operations, thus providing efficient fixed-point arithmetic on ciphertexts. Its advantage is prominent in the fields of privacy-preserving data analysis and machine learning. In a secure genome analysis competition *iDash*, for instance, most of the winners and runner-ups on the HE track have employed CKKS since 2017 [WTW<sup>+</sup>18, KJT<sup>+</sup>20, JHK<sup>+</sup>20]. However, its performance is still far from satisfactory for industry practitioners [Cra19, YZLT19, ZLX<sup>+</sup>20, BHS19, HLF<sup>+</sup>19]. Bootstrapping, the most inefficient operation in CKKS, requires, for instance, more than 60 seconds in a conventional PC environment [CHK<sup>+</sup>18] on a 128-bit security parameter set.

In this paper, we address these challenges by improving the performance of CKKS with a Residue Number System (RNS) [CHK<sup>+</sup>19], one of the most efficient FHE schemes for many applications. Furthermore, we strive to maximize the parallelization of RLWE-based FHE operations by exploiting a high-performance commodity platform, the GPU. That is, all of the operations of CKKS are implemented here to run on GPUs, including the HE multiplication and bootstrapping steps, which are correspondingly the most frequently used primitive operation and the slowest one.

Through an analysis, we discover that RLWE-based FHE operations have high memory bandwidth and capacity requirements. Most RLWE-based FHE schemes require many evaluation keys for manipulating ciphertexts (e.g., multiplication key and rotation keys); the key sizes are large as each is a ciphertext of a certain value related to the secret key. When examining the multiplication operation of CKKS (HMULT), we observe that the arithmetic intensity (OP/B, operation per byte) of HMULT's primary functions is low. Hence, they are not bottlenecked by the limited number of arithmetic units (compute-bound) but by the limited memory bandwidth (memory-bound) on modern GPUs. In particular, Tensor-product and Inner-product operations during key-switching exhibit very low arithmetic intensity levels (lower than 3 OP/B in Figure 2(b)). We also identify that most existing performance optimization techniques incur further increases in the memory bandwidth and capacity requirements; these include RNS-decomposition [BEHZ16a], efficient modup/down operations [CHK+19], improved linear transformation [HHC19], and efficient bootstrapping [HK20]. In particular, using a large decomposition number (dnum) greatly increases the memory capacity and bandwidth requirement.

These key observations lead us to devise memory-centric optimizations to improve the performance of CKKS on GPUs substantially. First, we fuse the functions that compose an individual HE operation, such as HMULT (intra-HE-fusion), and those across HE operations (inter-HE-fusion), by which we reduce accesses to the main memory (global memory) on the GPU. Second, in contrast to earlier work that involves a tradeoff between the computation cost and the multiplicative level (the number of subsequent HMULT operations on a ciphertext) [HK20], we also consider the main-memory bandwidth and capacity requirements while finding the optimal dnum for HMULT.

Owing to the aforementioned memory-centric optimizations, our HMULT and rescaling implementations perform  $7.02\times$  and  $1.36\times$  better, respectively, against a recently published result [BHM $^+$ 20] while using an identical GPU generation. We are the first to report the performance of bootstrapping in CKKS implemented on a GPU after applying recently proposed algorithm-level optimizations [HK20]. The proposed GPU implementation exceeds the speed of a single-thread CPU implementation by  $257\times$ . The wall-clock time for bootstrapping is reduced to 526.96ms in a 173-bit security parameter set with 65,536 slots and with 19-bit precision bit, which translates into 0.423us in terms of the amortized time per bit. Our result is superior by orders of magnitude to recent works that produce 298us [HK20] and 519us [CCS19] with 128-bit security parameter sets. To demonstrate the effectiveness of the proposed optimizations at an application level, we implement Logistic Regression identically to an earlier study [HHCP19] on a GPU. The evaluation confirms

that compared to the implementation on an 8-threaded CPU, there is a  $40.0 \times$  improvement (from 31.0 to 0.775 seconds per iteration) in speed when training with the same data used in the aforementioned earlier work [HHCP19].

Finally, we propose what is termed the 'amortized FHE-mult' time as a new unit of measurement for comparing HE multiplication performance. Amortized FHE-mult refers to the average time required per multiplication when an unlimited number of HMULTs are possible by bootstrapping. We calculate this time by measuring the average HMULT time plus the bootstrapping time divided by the maximum number of subsequent multiplications between two bootstrapping operations. The amortized FHE-mult time of our implementation is 24.35 ms, with which we believe that practical privacy-preserving applications can be developed.

#### 2 Background

#### 2.1 Notation for Homomorphic Encryption

We follow the notation definition in an earlier study [HK20] with minor modifications. For a polynomial ring  $\mathcal{R}=\mathbb{Z}[X]/(X^N+1)$ , where N is a power-of-two integer, we denote the residue ring modulo an integer q as  $\mathcal{R}_q=\mathcal{R}/q\mathcal{R}$ .  $\chi_{key}$  is the distribution of the secret key and  $\chi_{err}$  is the error distribution over  $\mathcal{R}$ .  $a \stackrel{\$}{\leftarrow} S$  means that a is sampled from set S uniformly or distribution S. We denote closed and open intervals using parentheses and brackets (e.g.,  $[a,b)=\{n\in\mathbb{Z}|a\leq n< b\}$ ).  $[\cdot]_q$  denotes the modular reduction by q, respectively. We represent an element in  $\mathcal{R}$  as  $m(X)=\sum_{i=0}^{N-1}m_iX^i$  and an element in  $\mathcal{R}_q$  as  $[m(X)]_q=\sum_{i=0}^{N-1}[m_i]_qX^i$ . We extend this notation for the RNS basis. For  $\mathcal{C}_i=\{q_0,\ldots,q_i\}$ , where the  $\{q_j\}_{0\leq j\leq i}$  values are coprime to each other, we define  $[s(X)]_{\mathcal{C}_i}$  as  $([s(X)]_{q_0},\cdots,[s(X)]_{q_i})\in\prod_{j=0}^i\mathcal{R}_{q_j}$ . We denote two disjoint subsets of set Y as  $\mathcal{S}_Y$  and  $\mathcal{S}_Y'$ .  $\odot$  denotes Hadamard multiplication. A concatenation of two vectors or sets is denoted as ||.  $L(\ell)$  represents the maximum (current) level of a ciphertext, the number of multiplications one can perform on the ciphertext without decryption. Let  $\hat{q}_{\ell,j}=\prod_{i=0}^\ell n_{i\neq j} q_j$ , where we omit the first subscript  $\ell$  when  $\ell=L$ .

#### 2.2 Polynomial Arithmetic in CKKS

Each ciphertext of CKKS is represented as a pair of polynomials of degree < N in  $\mathcal{R}_Q = \mathbb{Z}_Q[X]/(X^N+1)$  and a FHE operation consists of polynomial operations. Given that polynomial degree N is very high (e.g., degree  $N=2^{16}$  or  $2^{17}$ ) and the coefficient size is very big (e.g.,  $\log Q=2,000$ ), this type of polynomial arithmetic is very costly in FHE. For example, FHE-mult [CLP17, Cry20, HS14] becomes slower by a factor of thousands in terms of latency, compared to the native multiplication in the unencrypted domain.

Due to the high multiplication cost between polynomials, RLWE-based FHE schemes [BEHZ16a, CHK+19, BPA+19] typically have their own variants with the Residue Number System (RNS) [GHS12] to reduce their computational cost. First, by exploiting the Chinese Remainder Theorem (CRT), they represent each big-integer coefficient as a set of residues, each being a coefficient modulo a distinct prime number. Multiplication between two big integers is translated into point-wise multiplication between the two sets of residues, avoiding expensive multi-word arithmetic.

Second, they use Number Theoretic Transform (NTT) [AB75, Har14] and its inverse transformation (iNTT) for polynomial ring multiplication. NTT is a variant of Discrete Fourier Transform (DFT) [CCF<sup>+</sup>67] performed on a finite field of integers. Let  $\omega_{q_i}$  be the primitive N-th root of unity in  $R_{q_i}$ . For a polynomial  $[a(X)]_{q_i} \in \mathcal{R}_{q_i}$ , the NTT function NTT( $[a(X)]_{q_i}$ ) returns ( $[a(\omega_{q_i}^0)]_{q_i}$ ,  $\cdots$ ,  $[a(\omega_{q_i}^{N-1})]_{q_i}$ ) $\in (\mathbb{Z}_{q_i}^*)^N$ . The inverse NTT function iNTT takes the output of NTT and returns  $[a(X)]_{q_i}$ .

A naïve multiplication of the two polynomials  $a(X) = \sum_{i=0}^{N-1} a_i X^i, b(X) = \sum_{i=0}^{N-1} b_i X^i \in \mathcal{R}_{q_i}$  outputs a polynomial  $c(X) = \sum_{i=0}^{N-1} c_i X^i \in \mathcal{R}_{q_i}$  whose coefficients  $(c_0, \ldots, c_{N-1})$  are a negacylic convolution of two sequences  $(a_0, \ldots, a_{N-1})$  and  $(b_0, \ldots, b_{N-1})$ . The negacyclic convolution is replaced with two NTTs performed on each integer sequence, one element-wise modular multiplication between the two sequences in the NTT domain and one iNTT on the output of the element-wise multiplication. Because the computational complexity levels of NTT and iNTT are  $\mathcal{O}(N \log N)$  and the element-wise multiplication is  $\mathcal{O}(N)$ , the total complexity is reduced from  $\mathcal{O}(N^2)$  to  $\mathcal{O}(N \log N)$ .

For a polynomial with a RNS basis  $\mathcal{C}_i = \{q_0, ..., q_i\}$ , NTT and iNTT are applied to each modulus. We extend the notations NTT(·) and iNTT(·); given  $[a(X)]_{\mathcal{C}_i}$ , we denote  $[a]_{\mathcal{C}_i} = \text{NTT}([a(X)]_{\mathcal{C}_i}) = (a^{(0)}, a^{(1)}, \cdots, a^{(i)})$ , where  $a^{(j)} = \text{NTT}([a(X)]_{q_j})$ . Similarly, we denote iNTT( $[a]_{\mathcal{C}_i} = [a(X)]_{\mathcal{C}_i}$ . Then,  $[a(X)]_{\mathcal{C}_i} \cdot [b(X)]_{\mathcal{C}_i}$  equals iNTT( $[a]_{\mathcal{C}_i} \odot [b]_{\mathcal{C}_i}$ ). Henceforth, we omit the subscript for simplicity (e.g.,  $a \odot b$ ).

#### 2.3 RNS Basis Conversion and Decomposition

We target a recent RNS variant of the CKKS scheme [HK20]; it is an improved version of [CHK $^+$ 19], which reduces the operation complexity by adopting a generalized key-switching technique through RNS decomposition. Throughout this paper, we refer to this scheme as CKKS.

We describe RNS basis decomposition for the generalized key-switching and the basis conversion in CKKS. Fast basis conversion (Conv) converts the RNS basis of a polynomial into a new basis that is coprime to the original basis [CHK<sup>+</sup>19, BEHZ16a]. It is used in approximate modulus raising (ModUp) and approximate modulus reduction (ModDown), extending and shrinking the RNS basis of a polynomial, respectively.

Let  $\mathcal{B} = \{p_0, \dots, p_{k-1}\}$ ,  $\mathcal{C}_i = \{q_0, \dots, q_i\}$  for  $i \in [0, L]$ , where  $\{p_j\}_{j \in [0, k)}$ ,  $\{q_j\}_{j \in [0, L]}$  are coprime to each other. Let  $\hat{Q}_j''' = \prod_{q_i \in \mathcal{S}_{\mathcal{C}_L}} q_i \times \prod_{p_i \in \mathcal{S}_{\mathcal{B}} \wedge i \neq j} p_i$  and  $\hat{Q}_j'' = \prod_{q_i \in \mathcal{S}_{\mathcal{C}_L} \wedge i \neq j} q_i \times \prod_{p_i \in \mathcal{S}_{\mathcal{B}}} p_i$ . Conv(see Algorithm 1) changes the basis of an input polynomial  $[a(X)]_{\mathcal{S}_{\mathcal{C}_L} \cup \mathcal{S}_{\mathcal{B}}}$  to  $\mathcal{S}_{\mathcal{C}_L}' \cup \mathcal{S}_{\mathcal{B}}'$  approximately [BEHZ16a, CHK<sup>+</sup>19].

Given an integer dnum, let  $\alpha = (L+1)/\text{dnum}$  (for simplicity, we assume that (L+1) is divided into dnum). The parameter dnum divides the basis  $\mathcal{C}_L$  into the bases  $\{\mathcal{C}_i' = \{q_j\}_{j \in A_i = [i\alpha, i\alpha + \alpha)}\}$ , each having  $\alpha$  primes [HK20].

For a given level  $\ell$  of a ciphertext, let  $\beta$  be  $\lceil (\ell+1)/\alpha \rceil \leq$  dnum. Before key-switching, CKKS [HK20] first decomposes the RNS basis  $\mathcal{C}_{\ell}$  of a polynomial into  $\{\mathcal{C}_i'\}_{i \in [0,\beta)}$ , each of which is then extended to basis  $\mathcal{D}_{\beta}$  where  $\mathcal{D}_i$  is defined as  $\mathcal{B} \bigcup (\bigcup_{0 \leq j < i} \mathcal{C}_j')$ . After key-switching, the basis is reduced to  $\mathcal{C}_{\ell}$ .

We define  $P = \prod_{i=0}^{k-1} p_i, Q' = \prod_{i=\ell+1}^{\alpha\beta-1} q_i, \ \hat{Q} = PQ', \ \{Q'_j = \prod_{i=j\alpha}^{(j+1)\alpha-1} q_i\}_{j \in [0,\text{dnum})}, \ \text{and} \ \hat{Q}_j = \prod_{i=0 \land i \neq j}^{\text{dnum}-1} Q'_i.$  The decomposition algorithm (Dcomp), ModUp, and ModDown are shown in Algorithm 3, Algorithm 2, and Algorithm 4, respectively.

Please refer to Appendix D for more details.

```

Algorithm 1: \operatorname{Conv}_{\mathcal{S}_{\mathcal{C}_L} \cup \mathcal{S}_{\mathcal{B}} \to \mathcal{S}'_{\mathcal{C}_L} \cup \mathcal{S}'_{\mathcal{B}}}([a(X)]_{\mathcal{S}_{\mathcal{C}_L} \cup \mathcal{S}_{\mathcal{B}}}) (Fast basis conversion)

1 for q_i \in \mathcal{S}'_{\mathcal{C}_L} \cup \mathcal{S}'_{\mathcal{B}} // we use q_i to represent all the elements in \mathcal{S}'_{\mathcal{B}}

2 \left| \begin{array}{c} [\tilde{a}(X)]_{q_i} \leftarrow \left[ \sum_{q_j \in \mathcal{S}_{\mathcal{C}_L}} [[a(X)]_{q_j} \cdot \hat{Q}''^{-1}]_{q_j} \cdot [\hat{Q}''_j]_{q_i} \right]_{q_i} \\ 3 & \left[ \bar{a}(X)]_{q_i} \leftarrow \left[ \sum_{p_j \in \mathcal{S}_{\mathcal{B}}} [[a(X)]_{p_j} \cdot \hat{Q}'''^{-1}]_{p_j} \cdot [\hat{Q}'''_j]_{q_i} \right]_{q_i} \\ 4 & \left[ \tilde{a}(X)]_{q_i} \leftarrow [\tilde{a}(X)]_{q_i} + [\bar{a}(X)]_{q_i} \end{array}\right.

```

- 5 end for

- 6 return  $[\tilde{a}(X)]_{\mathcal{S}'_{\mathcal{B}} \cup S'_{\mathcal{C}_L}} = [\tilde{a}(X)]_{\mathcal{S}'_{\mathcal{B}}} ||[\tilde{a}(X)]_{\mathcal{S}'_{\mathcal{C}_L}}$

#### **Algorithm 2:** $ModUp_{C'_i \to D_\beta}([a]_{C'_i})$

```

\begin{array}{l} \mathbf{1} \ ([a(X)]_{\mathcal{C}_i'}) \leftarrow \mathbf{i} \mathbf{N} \mathbf{T} \mathbf{T} ([a]_{\mathcal{C}_i'}) \\ \mathbf{2} \ (\tilde{a}^{(j)})_{j \in A_i} = (a^{(j)})_{j \in A_i} \\ \mathbf{3} \ [\tilde{a}(X)]_{\mathcal{D}_{\beta} - \mathcal{C}_i'} \leftarrow \mathbf{Conv}_{\mathcal{C}_i' \to \mathcal{D}_{\beta} - \mathcal{C}_i'} \ ([a(X)]_{\mathcal{C}_i'}) \\ \mathbf{4} \ (\tilde{a}^{(j)})_{j \in ([0,k+\alpha\beta-1]-A_i)} \leftarrow \mathbf{N} \mathbf{T} \mathbf{T} ([\tilde{a}(X)]_{\mathcal{D}_{\beta} - \mathcal{C}_i'}) \\ \mathbf{5} \ \mathbf{return} \ [\tilde{a}]_{\mathcal{D}_{\beta}} = (\tilde{a}^{(0)}, \cdots, \tilde{a}^{(k+\alpha\beta-1)}) \end{array}

```

#### **Algorithm 3:** $\mathsf{Dcomp}(d = (d^{(0)}, \dots, d^{(\ell)}))$

```

\begin{array}{l} \mathbf{1} \ d^{(j)} \leftarrow 0 \ \forall j \in [\ell+1, \alpha\beta-1] \\ \mathbf{2} \ d^{(i)}_{j} \leftarrow d^{(j\alpha+i)} \cdot [Q']_{q_{j\alpha+i}} \cdot [\hat{Q}_{j}^{-1}]_{q_{j\alpha+i}} \ \ \forall i \in [0, \alpha-1], \forall j \in [0, \beta-1]. \\ \mathbf{3} \ d_{j} \leftarrow (d^{(i)}_{j})_{i \in [0, \alpha-1]} \ \forall j \in [0, \beta-1] \\ \mathbf{4} \ \mathbf{return} \ \vec{d} = (d_{j})_{j \in [0, \beta-1]} \end{array}

```

#### Algorithm 4: Approximate Modulus Reduction

```

\begin{array}{lll} \mathbf{1} \ \mathbf{procedure} \ \mathsf{ModDown}_{\mathcal{D}_{\beta} \to \mathcal{C}_{\ell}}(\tilde{b}^{(0)}, \ \tilde{b}^{(1)}, \ \dots, \ \tilde{b}^{(k+\alpha\beta-1)}) \\ \mathbf{2} & | \ [\tilde{b}]_{\mathcal{D}_{\beta} - \mathcal{C}_{\ell}} \leftarrow (\tilde{b}^{(0)}, \ \dots, \ \tilde{b}^{(k-1)}, \tilde{b}^{(k+\ell)}, \ \dots, \ \tilde{b}^{(k+\alpha\beta-1)}) \\ \mathbf{3} & | \ [\tilde{b}(X)]_{\mathcal{D}_{\beta} - \mathcal{C}_{\ell}} \leftarrow \mathbf{iNTT}([\tilde{b}]_{\mathcal{D}_{\beta} - \mathcal{C}_{\ell}}) \\ \mathbf{4} & | \ [\tilde{a}(X)]_{\mathcal{C}_{\ell}} \leftarrow \mathbf{Conv}_{\mathcal{D}_{\beta} - \mathcal{C}_{\ell} \to \mathcal{C}_{\ell}}([\tilde{b}(X)]_{\mathcal{D}_{\beta} - \mathcal{C}_{\ell}}) \\ \mathbf{5} & | \ [\tilde{a}]_{\mathcal{C}_{\ell}} \leftarrow \mathbf{NTT}([\tilde{a}(X)]_{\mathcal{C}_{\ell}}) \\ \mathbf{6} & | \ \mathbf{for} \ 0 \leq j \leq \ell \ \mathbf{do} \\ \mathbf{7} & | \ b^{(j)} = [\hat{Q}^{-1}]_{q_{j}} \cdot (\tilde{b}^{(k+j)} - \tilde{a}^{(j)}) \ (\mathbf{mod} \ q_{j}) \\ \mathbf{8} & | \ \mathbf{end} \\ \mathbf{9} & | \ \mathbf{return} \ (b^{(0)}, \dots, b^{(\ell)}) \\ \mathbf{10} & \ \mathbf{end} \ \mathbf{procedure} \end{array}

```

#### 2.4 Description of CKKS operations

We compactly describe CKKS [HK20] and its core operations. Let  $Q_i = \prod_{j=0}^i q_j$ .  $Q_L$  is termed the *ciphertext modulus*. CKKS encodes message  $\vec{z}$ , a vector of N/2 complex numbers, into a polynomial  $m(X) \in \mathcal{R}_Q$ , called *plaintext*. We refer to each position of a complex value in a message as a *slot*. The encoding step is as follows: (1) performing the inverse Discrete Fourier Transform (iDFT) on  $\vec{z}$ , (2) extracting the real and imaginary parts to concatenate the two, and (3) scaling up by multiplying with a scalar value  $\Delta$  (called the *scaling factor*), followed by a rounding operation. A larger  $\Delta$  increases the message precision but also requires larger primes  $q_i \in \mathcal{C}_L$ , lowering the security bit with others being equal. Typical values of  $\Delta$  range from  $2^{40}$  to  $2^{50}$ .

Let a secret key be  $s(X) \stackrel{\$}{\leftarrow} \chi_{\text{key}}$  and a plaintext be m(X), whose corresponding NTT representations are  $s = [s]_{\mathcal{C}_L} \leftarrow \text{NTT}([s(X)]_{\mathcal{C}_L})$  and  $m = [m]_{\mathcal{C}_L} \leftarrow \text{NTT}([m(X)]_{\mathcal{C}_L})$ . Let an evaluation key be  $\mathbf{evk} = (\mathbf{evk}_i)_{i \in [0, \text{dnum})}$ , where  $\mathbf{evk}_i = (evk_i^{(j)} = (a_{evk_i}^{(j)}, b_{evk_i}^{(j)}))_{j \in [0, k+L]} \in \prod_{n=0}^{k-1} ((\mathbb{Z}_{p_n}^*)^N)^2 \times \prod_{n=0}^L ((\mathbb{Z}_{q_n}^*)^N)^2$  such that  $(a_{evk_i}^{(j)}, b_{evk_i}^{(j)})$  are a pair of polynomials in the NTT domain.

We represent a level  $\ell$  ciphertext **ct** as a pair of polynomials in the NTT domain  $(a,b) \in (\prod_{j=0}^{\ell} (Z_{q_{\ell}}^*)^N)^2$  rather than the RNS domain  $([a(X)]_{\mathcal{C}_{\ell}}, [b(X)]_{\mathcal{C}_{\ell}})$ . CKKS encrypts

m(X) as a level L ciphertext  $\mathbf{ct} = (a, b) \leftarrow \mathtt{RLWE}(s, m)^1$ , where  $(a \stackrel{\$}{\leftarrow} \prod_{j=0}^L (\mathbb{Z}_{q_j}^*)^N, b \leftarrow a \odot s + e + m)$  and  $e \stackrel{\$}{\leftarrow} \chi_{\mathsf{err}}$ . More information is provided in Subsection D.2.

An FHE-mult between two ciphertexts (HMULT) followed by rescaling, a function adjusting the scaling factor  $\Delta$  of the message, reduces one level of the ciphertext. For an HE circuit reducing the input ciphertext level by d, we refer to d as the multiplicative depth.

We provide the details of HMULT and the other FHE operations in Algorithm 5 - 9. CMULT(ct, m) returns (ma, mb), where  $(a, b) \leftarrow$  ct. HMULT (HADD) multiplies (adds) ct<sub>0</sub> by (and) ct<sub>1</sub>. RESCALE performs the rescaling operation for ct. HROTATE(ct, sn, ebk) rotates the message of ct according to the rotation index sn, which is translated into a Frobenius map in the corresponding plaintext:  $m(X) \rightarrow m(X^{5^{sn}})$ . The function FrobeniusMap(m, sn) performs  $m(X) \mapsto m(X^{5^{sn}})$  in the NTT domain [HK20]. For the given  $\{m^{(i)} = (m_j^{(i)})_{j \in [0,N-1]}\}_{i \in [0,\ell]}$ , it generates  $\{m'^{(i)} = ((m_{\pi_n^{-1}(j)}^{(i)})_{j \in [0,N-1]}\}_{i \in [0,\ell]}$ , where  $\pi_n(x) = ([5^n(2x+1)]_{2N}-1)/2$ , which is a permutation. KeySwitch decomposes the input polynomial  $[d]_{\mathcal{C}_\ell}$  into  $[d_j]_{\mathcal{C}_j'}$ , where  $j \in [0,\beta)$ , extends the moduli of the decomposed parts using ModUp, multiplies them by an evaluation key, and finally reduces the moduli to the original level  $\ell$  using ModDown. Throughout the paper, we refer to step 3 in Algorithm 9 as the Inner-product.

#### Algorithm 9: KeySwitch( $[d]_{\mathcal{C}_{\ell}}$ ,evk) performs key-switching over d

```

\begin{array}{l} \mathbf{1} \  \, \vec{d} \leftarrow \mathtt{Dcomp}(d), \, (d_j)_{j \in [0,\beta-1]} \leftarrow \vec{d} \\ \mathbf{2} \  \, [\tilde{d}_j]_{\mathcal{D}_{\beta}} = (\tilde{d}_j^{(0)}, \tilde{d}_j^{(1)}, \cdots, \tilde{d}_j^{(k+\alpha\beta-1)}) \leftarrow \mathtt{ModUp}([d_j]_{\mathcal{C}_j'}) \  \, \text{for} \  \, j \in [0,\beta-1] \\ \mathbf{3} \  \, ([c_0]_{\mathcal{D}_{\beta}}, [c_1]_{\mathcal{D}_{\beta}}), \, \text{where} \  \, (c_0^{(i)}, c_1^{(i)}) = \Sigma_{j=0}^{\beta-1} \tilde{d}_j^{(i)} \odot \mathbf{evk}_j^{(i)} \  \, \text{for} \  \, i \in [0,k+\alpha\beta-1] \\ \mathbf{4} \  \, ([c_0]_{\mathcal{C}_{\ell}}, [c_1]_{\mathcal{C}_{\ell}}) \leftarrow (\mathtt{ModDown}([c_0]_{\mathcal{D}_{\beta}}), \mathtt{ModDown}([c_1]_{\mathcal{D}_{\beta}})) \\ \mathbf{5} \  \, \mathbf{return} \  \, ([c_0]_{\mathcal{C}_{\ell}}, [c_1]_{\mathcal{C}_{\ell}}) \end{array}

```

#### 2.5 Bootstrapping in CKKS

Before the level of a ciphertext is depleted by consecutive operations, bootstrapping must be performed on the ciphertext to increase its level and to allow more FHE operations on the ciphertext. We briefly explain the CKKS bootstrapping algorithm here [CHK<sup>+</sup>18, HK20]. **Modulus Raising:** Let **ct** be a ciphertext given by encrypting the plaintext m(X). Let the current modulus of **ct** be  $q = q_0$  having a zero level. Our goal is to increase the modulus (or, level). First, the modulus of **ct** is increased to  $Q_L$ , the modulus of a freshly

<sup>&</sup>lt;sup>1</sup>The process of encryption using a public key rather than a private key is different from this, but the form of the result is the same. However, there is a difference that the size of the included error increases.

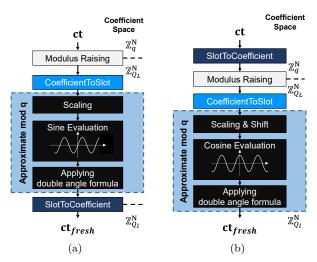

**Figure 1:** Flow diagram of (a) the original CKKS bootstrapping algorithm [CHK<sup>+</sup>18] and (b) ours adopting cosine evaluation in [HK20] and slim bootstrapping in [CH18].

encrypted ciphertext, producing  $\mathbf{ct}'$ . Although the level is increased, it adds the error polynomial  $q \cdot I(X)$  to the plaintext:  $Decrypt(\mathbf{ct}') = t(X) = m(X) + q \cdot I(X)$ , where I(X) is a polynomial whose coefficients are integers bounded to a small integer K, which is determined by the secret key distribution. To remove the error, we apply the approximate modulo operation in a homomorphic manner.

**Coefficient ToSlot:** Let the plaintext  $t(X) = t_0 + t_1X + t_2X^2 + \ldots + t_{N-1}X^{N-1}$  be the decryption of  $\mathbf{ct'}$  in Modulus Raising and its decoding be  $\vec{z}$ . The goal of Coefficient ToSlot is to compute  $\mathbf{ct_1}$  and  $\mathbf{ct_2}$ , which contain messages  $\vec{z}_1 = (t_0, t_1, \ldots, t_{N/2-1})$  and  $\vec{z}_2 = (t_{N/2}, t_{N/2+1}, \ldots, t_{N-1})$ , respectively.  $\mathbf{ct_1}$  and  $\mathbf{ct_2}$  are computed by evaluating the encoding circuit, the linear transformation on  $\mathbf{ct}$ :

$$\vec{z}_1 = 1/N \cdot (\overline{\mathbf{V}}^T \vec{z} + \mathbf{V}^T \overline{\vec{z}}), \ \vec{z}_2 = 1/N \cdot (\overline{\mathbf{W}}^T \vec{z} + \mathbf{W}^T \overline{\vec{z}})$$

where

$$\mathbf{V} = \begin{pmatrix} 1 & \omega_0 & \cdots & \omega_0^{\frac{N}{2} - 1} \\ 1 & \omega_1 & \cdots & \omega_1^{\frac{N}{2} - 1} \\ \vdots & \vdots & \ddots & \vdots \\ 1 & \omega_{\frac{N}{2} - 1} & \cdots & \omega_{\frac{N}{2} - 1}^{\frac{N}{2} - 1} \end{pmatrix} \text{ and } \mathbf{W} = \begin{pmatrix} \omega_0^{\frac{N}{2}} & \omega_0^{\frac{N}{2} + 1} & \cdots & \omega_0^{N-1} \\ \omega_1^{\frac{N}{2}} & \omega_1^{\frac{N}{2} + 1} & \cdots & \omega_1^{N-1} \\ \vdots & \vdots & \ddots & \vdots \\ \omega_{\frac{N}{2} - 1}^{\frac{N}{2}} & \omega_{\frac{N}{2} - 1}^{\frac{N}{2} + 1} & \cdots & \omega_{\frac{N}{2} - 1}^{N-1} \end{pmatrix}.$$

Instead of performing two linear transformations, the relationships  $i\mathbf{V} = \mathbf{W}$  and  $\overline{\mathbf{V}^T} \vec{z} = \mathbf{V}^T \overline{\vec{z}}$  are exploited, requiring only one linear transform to produce  $\overline{\mathbf{V}}^T \vec{z}$ ; the following homomorphic conjugation and addition/subtraction compute the other terms. Approximated modulo operation: For the two ciphertexts  $\mathbf{ct}_1$  and  $\mathbf{ct}_2$ , we want to perform modular reduction on each element of their messages:  $(t_i \mod q)$  for all i. However, because the modular reduction operation is not available in FHE, twofold approximation of the modulo operation is used instead. First, the modulo q operation is approximated as a scaled sine function, such as  $f(t) = q/2\pi \sin(2\pi t/q)$  [CHK+18]. This exploits the facts that each value  $t_i$  in message  $\vec{z}_1$  and  $\vec{z}_2$  is distributed near  $q \cdot I$  for an integer  $I \in (-K, K)$  for a small K, and the scaled sine function resembles the modulo operation near  $q \cdot I$ . Second, as the sine function is also not available in FHE, it is approximated as a polynomial. We adopted a recent bootstrapping algorithm from [HK20]. First, it approximates not the sine but the cosine function by shifting  $\mathbf{ct}_1$  and  $\mathbf{ct}_2$ . Also, it uses polynomial interpolation with the Chebyshev polynomial basis to approximate the

cosine function in addition to adopting the double-angle formula. We use one of their parameter sets for bootstrapping; we evaluate a 31-degree polynomial and then apply the double-angle formula three times, approximating  $f(t) = \cos(24\pi t)$ . With applying the cosine evaluation to  $\mathbf{ct}_1$  and  $\mathbf{ct}_2$ , we obtain two output ciphertexts  $\mathbf{ct}_1'$  and  $\mathbf{ct}_2'$  whose messages are  $\vec{z}_1'$  and  $\vec{z}_2'$ , respectively. Our cosine evaluation step has a multiplicative depth of 11.

**SlotToCoefficient:** This is the opposite of CoefficientToSlot. With  $\mathbf{ct}_1'$  and  $\mathbf{ct}_2'$ , we compute an output ciphertext,  $\mathbf{ct}_{fresh}$ , which contains message  $\vec{z}_{fresh}$ , by evaluating a linear transformation, as shown below:

$$\vec{z}_{fresh} = \mathbf{V}\vec{z}_1' + \mathbf{W}\vec{z}_2' = \mathbf{V}(\vec{z}_1' + i\vec{z}_2')$$

Here,  $\vec{z}_{fresh}$  is approximately equal to the message of **ct** before Modulus Raising.

We also adopt the additional technique of *slim bootstrapping* from [CH18], which reorders the bootstrapping process (see Figure 1) from (Modulus Raising, CoefficientToSlot, Cosine evaluation, SlotToCoefficient) to (SlotToCoefficient, Modulus Raising, CoefficientToSlot, Cosine evaluation). By postponing Modulus Raising, the computational cost of SlotToCoefficient decreases as the ciphertext level of the input to SlotToCoefficient decreases.

We also use efficient CoefficientToSlot and SlotToCoefficient proposed in [HHC19]. That study adopts the Cooley-Tukey FFT algorithm [CT65] for linear transform in CoefficientToSlot and SlotToCoefficient. The DFT algorithm can be expressed in the form of multiplication between DFT matrix  $\mathbf{D}$  and input vector  $\vec{v}$ . The computational complexity of directly computing  $\mathbf{D} \cdot \vec{v}$  is  $\mathcal{O}(N^2)$ . By adopting the Cooley-Tukey FFT algorithm,  $\mathbf{D}$  can be decomposed into  $\log_2 N$  block-diagonal sparse matrices, reducing the total complexity to  $\mathcal{O}(N \log N)$ .

For a given radix r and degree N, they decompose  $\mathbf{V}_{rev}$ , which is a row-permuted  $\mathbf{V}$ , into  $\log_r(N/2)$  block-diagonal sparse matrices  $\{\mathbf{V}_i^{(r)}\}_{1\leq i\leq \log_r(N/2)}$  such that  $\mathbf{V}_{rev} = \mathbf{V}_1^{(r)}\mathbf{V}_2^{(r)}\dots\mathbf{V}_{\log_r(N/2)}^{(r)}$ . Each decomposed block-diagonal sparse matrix  $\mathbf{V}_i^{(r)}$  is a matrix having 2r-1 (when i>1) or r (when i=1) diagonals, with all other element values being zero. We refer to each diagonal of index i from matrix  $\mathbf{M}$  as a length-N/2 vector,  $diag_i(\mathbf{M})$  such that  $diag_i(\mathbf{M}) = (\mathbf{M}(0,i),\mathbf{M}(1,i+1),\dots,\mathbf{M}(N/2-1,N/2+i-1))$  where  $\mathbf{M}(i,j)$  refers to the (i,j) element of  $\mathbf{M}$ . The same decomposition technique applies to Coefficient ToSlot as well. For more details, see Appendix  $\mathbf{B}$ .

An important characteristic of the (2r-1) (or, r) diagonals of each decomposed block-diagonal sparse matrix is that their indices form an arithmetic progression. Using this property, [HHC19] adopts the Baby-step Giant-step algorithm, as in [HS15, CH18, CHK<sup>+</sup>18], reducing the number of FHE rotations required during each multiplication between a block-diagonal sparse matrix and a vector that is encrypted as a ciphertext.

Baby-step Giant-step algorithm: Each multiplication between a block-diagonal sparse matrix and the input vector is performed in a homomorphic-friendly way, exploiting the Baby-step Giant-step algorithm (BSGS) [HS15, CH18, CHK<sup>+</sup>18]. BSGS computes the matrix-vector multiplication via the summation of the products of plaintexts, each being an encoded diagonal, and the shifted input vectors, each being the message of a correspondingly rotated ciphertext.

Let a predetermined block-diagonal sparse matrix with n diagonals be  $\mathbf{M}$  and the input vector be  $\vec{v}$ , the message of the ciphertext  $\mathbf{ct}$ . Let  $rot_i(\vec{v})$  be an input vector shifted by i, the message of HROTATE( $\mathbf{ct}$ , i,  $\mathbf{evk}$ ). For l and t such that  $l \cdot t = n$ , BSGS computes  $\mathbf{M} \cdot \vec{v}$  as shown below, where the common difference of the arithmetic progression is one:

$$\mathbf{M} \cdot \vec{v} = \sum_{i=0}^{n-1} diag_i(\mathbf{M}) \odot rot_i(\vec{v}) = \sum_{i=0}^{l-1} \sum_{j=0}^{t-1} diag_{ti+j}(\mathbf{M}) \odot rot_{ti+j}(\vec{v})$$

$$= \sum_{i=0}^{l-1} rot_{ti} (\sum_{j=0}^{t-1} rot_{-ti} (diag_{ti+j}(\mathbf{M})) \odot rot_j(\vec{v}))$$

(1)

Given a radix r, by choosing l and t near  $\sqrt{n}$ , the number of rotations required for each SlotToCoefficient and CoefficientToSlot is reduced from  $\mathcal{O}(r\log_r n)$  to  $\mathcal{O}(\sqrt{r}\log_r n)$ , as each block-diagonal sparse matrix has 2r-1 (or, r) diagonals. We can choose any l and t with flexibility by adding zero diagonals [HHC19].

#### 3 CKKS: Baseline implementation

#### 3.1 Basic HE operations

We provide here the pertinent details of the baseline CPU and GPU implementation of CKKS. For readers unfamiliar with contemporary GPU architectures, we recommend reading Appendix A. There are four groups of functions that compose operations in CKKS: (1) element-wise RNS operations between polynomials, such as multiplication in the NTT domain, addition, and subtraction; (2) NTT and iNTT; (3) fast basis conversion (Conv) used in ModUp and ModDown [BEHZ16a, CHK+19]; and (4) Inner-product in key-switching. Throughout this paper, we use double-word (i.e., 64-bit) moduli such that  $\{q_i\}_{i\in[1,L]}$  are 52-bit and  $\{q_0, p_0, ..., p_k\}$  are 62-bit. Also, we layout input and output data contiguously in memory in a degree-first manner (i.e., a chunk of N residues of  $a^{(i)}$  are continuous for each i) so that the data become NTT-friendly [CLP17, HS14, CHK+19].

**RNS operation:** We refer to an *RNS operation* as a binary operation that takes residues as input and performs an element-wise operation on them, such as multiplication, addition, and subtraction. In our CPU implementation, each CPU thread takes two vectors with N residues (i.e.,  $a^{(i)}, b^{(i)} \in \mathcal{R}_{q_j}$ ) at a time and performs N RNS operations, as in [CLP17]. Then, the thread (or another thread in a multi-threaded, multi-core environment) takes another pair of two vectors with N residues, until  $(\ell+1) \times N$  RNS operations are complete by all threads. In contrast, our GPU implementation follows an earlier method in [BPA+19]; we launch  $(\ell+1) \times N$  threads for a single GPU kernel. Letting each GPU thread perform a single RNS operation, we exploit the massive thread-level parallelism available from modern GPUs, which can run hundreds of thousands of threads concurrently.

**NTT and iNTT:** For NTT and iNTT, in both CPU and GPU implementation, we exploit the David Harvey's NTT algorithm [Har14] along with the in-place Cooley-Tukey algorithm, which is commonly used in other works [CLP17, Sho16, HS14].

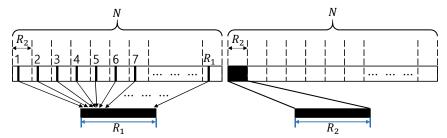

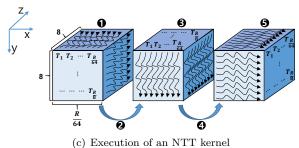

For the CPU implementation of NTT, we use the same approach as in the RNS operation, where each thread takes N residues (i.e.,  $a^{(i)}$  for a given i) at a time, and perform N-point NTT. For the GPU implementation, we use the hierarchical NTT implementation [KJPA20], which heavily exploits shared memory in GPUs while adopting an earlier approach in [GLD<sup>+</sup>08]. Specifically, for every (i)NTT with N residues, we use 8 per-thread (i)NTT kernels, as described in [KJPA20], where each thread in a kernel loads eight residues into the registers at a time. We launch kernels each performing radix-256 or radix-512 (i)NTT, where radix-k divides an N-point transformation into k interleaved N/k-point transformations. It uses shared memory as storage for the temporal output of each (i)NTT stage so that the N residues are loaded from and stored to global memory only once per kernel [GLD<sup>+</sup>08]. We launch two sequential GPU kernels for practical values of N ranging from  $2^{16}$  to  $2^{17}$ . See Appendix C for more details.

**ModUp and ModDown:** First, we explain the implementation of fast basis conversion. Given an input polynomial a(X) and RNS bases  $\mathcal{S}_1 = \mathcal{S}_{\mathcal{C}_L} \cup \mathcal{S}_{\mathcal{B}}$  and  $\mathcal{S}_2 = \mathcal{S}'_{\mathcal{C}_L} \cup \mathcal{S}'_{\mathcal{B}}$ ,

Algorithm 10: Baseline implementation of Inner-product in key-switching

a fast basis conversion  $\operatorname{Conv}_{\mathcal{S}_1 \to \mathcal{S}_2}([a(X)]_{\mathcal{S}_1})$  consists of two steps. Step 1 multiplies each input residue by  $\hat{Q}''_j^{-1} \mod q_j$  (or  $\hat{Q}'''_j^{-1} \mod p_j$ ) for the corresponding j. Then, step 2 computes each output residue via a multiply-accumulate (MAC) operation on  $|\mathcal{S}_1|$  input residues each multiplied by  $(\hat{Q}''_j \mod q_j(p_j))$  or  $(\hat{Q}'''_j \mod q_j(p_j))$  for the corresponding  $q_j$  (or  $p_j$ )  $\in \mathcal{S}_1$ , followed by a modular reduction with  $p_i$  (or  $q_i$ )  $\in \mathcal{S}_2$  (see Conv in Subsection 2.3).

In the CPU implementation of fast basis conversion, each thread takes N residues that are coefficients of  $[a(X)]_{q_j \text{ (or } p_j)}$ , where  $q_j$  (or  $p_j$ )  $\in \mathcal{S}_1$  serve as inputs, and performs the step 1. After all threads complete the first step, step 2 begins, where each thread computes N output residues; the inner-most loop, which performs MAC followed by modular reduction, computes one output residue at a time.

The GPU implementation of the fast basis conversion consists of two kernels (see Appendix C for details). The first kernel (called the *scaling* kernel) for step 1 launches  $|\mathcal{S}_1| \times N$  threads where each thread multiplies an input residue by a corresponding constant  $\hat{Q}_j^{\prime\prime\prime}(\hat{Q}_j^{\prime\prime\prime\prime}) \mod q_j$  ( $p_j$ ). The second kernel for step 2 launches  $|\mathcal{S}_2| \times N$  threads where a thread takes  $|\mathcal{S}_1|$  residues of a coefficient as inputs to compute one output. Throughout the accumulation, the partial sum resides in the registers held by the threads. When the accumulation process is completed, the thread performs modular reduction on the result. A prior work [BPA+19] implements fast basis conversion on a GPU but performs modular reduction right before the partial sum overflows; in contrast, we accumulate the partial sum into three double-word values (which are stored in the register file).

Both ModUp and ModDown exploit fast basis conversion, performing iNTT on the inputs of fast basis conversion and NTT on the outputs. The difference between them lies in the RNS operations coming after NTT. ModUp concatenates the output of NTT to its input with the original basis to extend the basis. ModDown (see Algorithm 4) subtracts the original input from the output of NTT and scales by  $\hat{Q}^{-1} \mod q_j$  (line 7). Because the subtraction and scaling after NTT are element-wise RNS operations, our CPU and GPU implementations use an identical approach when executing them as explained above.

Inner-product in key-switching: The baseline implementation of Inner-product in key-switching is shown in Algorithm 10. It includes the lazy modular reduction technique adopted in FHE libraries [CLP17, Cry20]. This technique performs wide MAC operations (i.e., the partial sum being 128-bit) instead of doing modular reduction  $\beta$  times.

In our CPU implementation, a thread loads three vectors of N residues, one from  $d_2^{(i)}$  and two from  $\mathbf{evk}_i$  for  $i \in [0, \beta)$  and then performs multiplication (line 4) or MAC (line 6) in an element-wise manner. This is repeated  $\beta$  times, followed by Barrett's modular reduction [Bar87] (lines 8 and 9). Our baseline GPU implementation launches three types of kernels: one for multiplication (line 4), another for MAC (line 6), and the third for

#### Algorithm 11: Evaluation of BSGS in Equation 1

```

1 ct :=(input ciphertext)

2 out :=(zero-initialized output ciphertext)

3 \mathbf{ptxt} := \{m_{i,j}\}_{i \in [0,l), j \in [0,t)}

// precomputed plaintexts

4 procedure

for j in [1,t) do

\mathbf{ct}_j = \mathtt{HROTATE}(\mathbf{ct}, j)

6

7

end

for i in [0, l) do

8

\mathbf{accum} = \mathtt{CMULT}(\mathbf{ct}, m_{i,0})

9

10

for j in [1,t) do

\mathbf{temp} = \mathtt{CMULT}(\mathbf{ct}_j, m_{i,j})

11

accum = HADD(temp, accum)

12

13

temp = HROTATE(accum, ti)

14

out = HADD(accum, out)

15

end

16

return out

17

18 end procedure

```

modular reduction (lines 8 and 9). Each of the three launches  $(\alpha\beta + k)N$  threads. In the first and the second kernel, each thread takes three residues as inputs, one from  $d_2^{(i)}$  and two from  $\mathbf{evk}_i$ . Then the thread multiplies the first input by the others, accumulates them into two 128-bit partial sums, and stores them as in the CPU implementation case. The last kernel reduces the 128-bit partial sums to 64-bits using Barrett's modular reduction.

#### 3.2 Baby-step Giant-step

Let a matrix  $\mathbf{M}$  be predetermined with l diagonals whose indices form arithmetic progression, and let vector  $\vec{v}$  be encrypted as a ciphertext  $\mathbf{ct}$ . In CKKS, the evaluation of BSGS in Equation 1, where  $rot_{-ti}(diag_{ti+j}(\mathbf{M}))$  is encoded as a plaintext  $m_{i,j}$  for each  $0 \le i < l, 0 \le j < t$ , is done as shown in Algorithm 11. This requires a distinct rotation key for each rotation index j, but we skip the notation here for simplicity.

We describe the implementation of the HE operations required in BSGS. CMULT is performed as two element-wise RNS operations as described in the previous section. HROTATE is mostly similar to HMULT for its key-switching, except that it includes a Frobenius map (see Section 2), which is a permutation in the NTT domain. For the implementation of the permutation with index n, where the  $\{j\}_{[0,N)}$ -th residue of a given input  $\{a^{(i)}\}_{[0,\ell]}$  is moved into the  $\pi_n(j)$ -th position, each CPU thread executes in-place permutation on N residues, whereas the GPU performs out-of-place permutation by launching  $(\ell+1)\times N$  threads such that the  $(i\times N+j)$ -th thread takes the j-th residue of  $a^{(i)}$ .

**Hoisting:** Halevi et al. [HS18] suggested reducing the computation cost of BSGS by applying *hoisting*. Hoisting reduces the required number of ModUp operations, when multiple HROTATE operations with different rotation indices are performed on the same ciphertext. Specifically, it restructures the HROTATE algorithm to perform ModUp first, before the Frobenius map. Below is the computation order in HROTATE with hoisting:

- 1. (PrecomputeModUp) Perform iNTT, fast basis conversion, and NTT on a of a ciphertext  $\mathbf{ct} = (a, b)$ .

- 2. (FastRotate) Perform the Frobenius map with rotation index *i*. Skip ModUp. Perform Inner-product, ModDown, and remaining functions required for HROTATE.

The modified HROTATE consists of two steps. When one needs to rotate a single ciphertext with different rotation indices, we perform ModUp only once on a ciphertext, after which we perform multiple FastRotate instead of HROTATE. The error bound of FastRotate remains identical to that of HROTATE; the error bound is proportional to the infinity norm  $\|\tilde{a}\|_{\infty}$ , where  $\tilde{a}$  is the reconstructed output of ModUp [CHK<sup>+</sup>19], and hoisting preserves the infinity norm (i.e., it changes only the order of the coefficients).

By applying the hoisting, one PrecomputeModUp is required immediately before the line 5 of Algorithm 11, whereas HROTATE in line 6 changes to FastRotate, reducing the required number of ModUp operations from (t-1)+(l-1) to 1+(l-1). We evaluate the performance improvement of bootstrapping with hoisting in Section 6.

### 4 Bottleneck Analysis of FHE-Mult

In this section, we show that the major FHE operations in CKKS are primarily limited by the global memory bandwidth of GPUs.

#### 4.1 Function-level Operation Complexity and Memory Access Analysis

First, we show the operational complexity and the number of global memory accesses of each function during a multiplication of CKKS (HMULT). We evaluate the operational complexity in terms of the number of integer multiplications and additions, as in [TLW19]. First, we count the number of modular multiplications (ModMuls) as well as the other operations and then convert the ModMuls into the number of multiplications and additions. We count one Barrett's ModMul [Bar87] (Shoup's ModMul [Sho16]) as four (three) multiplications and three (two) additions, using the methodologies explained in [TLW19]. For simplicity, we assume that the two input ciphertexts have the same level  $\ell$ , with  $\beta = (\ell+1)/\alpha$  without the ceiling function.

Prior work [HK20] showed the operation complexity of HMULT in CKKS for various values of dnum in terms of the number of ModMuls and showed that it is practical to choose a moderate dnum; however, they did not consider the high memory bandwidth requirement, which directly affects into the performance of HMULT, especially on GPUs. We assume that each modulus  $\{q_i\}_{0 \leq i \leq L}$  and  $\{p_j\}_{0 \leq j < k}$  is of the double-word type (8 bytes). We count the global memory accesses in unit of eight bytes. Also, we consider subtraction as signed addition.

**Tensor-product:** We exploit the Karatsuba algorithm [KO62], which is commonly used in many HE libraries [HS14, Cry20, CLP17]. It computes  $a_1 \odot a_0, b_1 \odot b_0, (a_0 + a_1) \odot (b_0 + b_1)$  first and then computes  $(d_2, d_1, d_0)$  (see Subsection 2.4) from them, reducing the number of polynomial multiplications from 4 to 3 at cost of three additions, which is inexpensive. This results in  $3(\ell+1)N$  ModMuls,  $4(\ell+1)N$  additions in total. For the memory accesses, four input polynomials are loaded and three output polynomials are stored such that  $4(\ell+1)N$  reads and  $3(\ell+1)N$  writes take place.

**RNS-Decomposition:** There are  $\alpha\beta N = (\ell+1)N$  ModMuls and  $2(\ell+1)N$  memory accesses in total for reads and writes (see Dcomp in Subsection 2.3).

**NTT & iNTT:** For a single execution of (i)NTT on the N residues of each  $\{a^{(i)}\}_{i\in[0,\ell]}$ , there are  $\log N$  stages, resulting in  $(N\log N)/2$  ModMuls and  $N\log N$  additions. The number of global memory accesses can be as high as  $2N\log N$  for the loading and storing the input and output, respectively, and N for the loading twiddle factors.

However, there are two more factors that affect the total number of memory accesses: the cache memory size of the processor and Shoup's ModMul [Sho16]. If the cache is large enough to accommodate the length-N input of (i)NTT, it does not have to access the global memory at each stage, reducing the memory accesses by up to a factor of  $1/\log N$ . Modern server-class CPUs have last-level cache memory of dozens of megabytes [AFK<sup>+</sup>19],

**Table 1:** Operation complexity and memory accesses required in HMULT with ciphertexts having level l < L and degree N. We converted the number of ModMuls into multiplications (muls) and additions (adds) to count total integer operations.  $\alpha = (L+1)/\text{dnum}$  and  $\beta = (\ell+1)/\alpha$ .

|                   | # of ModMuls                        | # of muls and adds                        | # of total integer ops                               | Memory accesses<br>(each 8B)              |

|-------------------|-------------------------------------|-------------------------------------------|------------------------------------------------------|-------------------------------------------|

| Tensor-product    | $3(\ell + 1)N$                      | $4(\ell + 1)N$                            | $25(\ell + 1)N$                                      | $7(\ell + 1)N$                            |

| RNS-decomposition | $(\ell+1)N$                         | -                                         | $7(\ell + 1)N$                                       | $2(\ell+1)N$                              |

| NTT               | $\beta(\alpha\beta + k)N(\log N)/2$ | $\beta(\alpha\beta + k)N(\log N)$         | $7\beta(\alpha\beta + k)N(logN)/2$                   | $\beta(\alpha\beta + k)(2N + N\log N)$    |

| iNTT              | $(2\alpha\beta + k)N(\log N)/2$     | $(2\alpha\beta + k)N(\log N)$             | $7(2\alpha\beta + k)N(\log N)/2$                     | $(2\alpha\beta + k)(2N + N\log N)$        |

| Inner-product     | $2(\alpha\beta + k)N$               | $(4\beta - 2)(\alpha\beta + k)N$          | $(4\beta + 12)(\alpha\beta + k)N$                    | $(11\beta - 4)(\alpha\beta + k)N$         |

| Conv (ModUp)      | $\beta(\alpha\beta + k - \alpha)N$  | $2\alpha\beta(\alpha\beta + k - \alpha)N$ | $(7\beta + 2\alpha\beta)(\alpha\beta + k - \alpha)N$ | $(\alpha\beta + \alpha\beta^2 + k\beta)N$ |

| Conv (ModDown)    | $2\alpha\beta N$                    | $4k\alpha\beta N$                         | $(4k + 14)\alpha\beta N$                             | $2(\alpha\beta + k)N$                     |

easily achieving such a reduction in memory accesses. In contrast, GPUs have a much smaller last-level cache of a few megabytes [NVI17] and can scarcely accommodate the input/output of (i)NTT. Therefore, the number of memory accesses required on a GPU to load an input polynomial of (i)NTT is between  $2N \log N$  and 2N.

Our baseline (i)NTT implementation [KJPA20] launches two GPU kernels, each of which performs radix- $\sqrt{N}$  (i)NTT, resulting in  $2N\log N/\log \sqrt{N}$  accesses for the input and output. Rather than Barrett's algorithm [Bar87], we adopt Shoup's ModMul, as implemented in [KJPA20], which is commonly used for (i)NTT to reduce the operational complexity of ModMuls [CLP17, HS14]. Using Shoup's method adds extra N memory accesses as it demands a precomputed value for each ModMul. iNTT is performed at the front of ModUp and ModDown, each being done  $\beta$  times for  $\alpha N$  residues and once for  $(\alpha \beta + k)N$  residues (see Subsection 2.3). NTT is performed on the output of the basis conversion in ModUp and ModDown, each done  $\beta$  times for  $(\alpha \beta + k - \alpha)N$  residues and once for  $\alpha \beta N$  residues.

**ModUp:** Because we count the operations in (i)NTT separately, we consider only fast basis conversion in ModUp and ModDown here. With the lazy modular reduction technique, one needs to perform modular reduction only once after computing a sum of product, as stated in Section 3. Therefore,  $\alpha\beta(\alpha\beta+k-\alpha)N$  multiplications,  $\alpha\beta(\alpha\beta+k-\alpha)N$  additions, and  $\beta(\alpha\beta+k-\alpha)N$  modular reductions are required in total. The number of memory accesses is  $\alpha\beta N$  for reads and  $\beta(\alpha\beta+k)N$  for writes in total.

Inner-product: As in ModUp, lazy modular reduction is applied to Inner-product in key-switching, resulting in  $2\beta(\alpha\beta+k)N$  multiplications,  $2(\beta-1)(\alpha\beta+k)N$  additions, and  $2(\alpha\beta+k)N$  modular reductions. The required memory accesses are  $2\beta(\alpha\beta+k)N$  for loading  $\{\mathbf{evk}_i\}_{0\leq i<\beta}$ ,  $\beta(\alpha\beta+k)N$  for loading  $\{d_{2,i}\}_{0\leq i<\beta}$ , and finally,  $4(\beta-1)(\alpha\beta+k)N$  and  $4\beta(\alpha\beta+k)N$  for loading and storing **accum** in Algorithm 10, respectively.

**ModDown:** There are  $k(\alpha\beta)N$  multiplications,  $k(\alpha\beta)N$  additions, and  $(\alpha\beta)N$  modular reductions for each of the two polynomials  $(a'_{accum}$  and  $b'_{accum})$ , which are the output of **Inner-product**. Meanwhile, there exist kN memory accesses for the loading of the input and  $(\alpha\beta + k)N$  for the storing of the output for each of the two polynomials.

We summarize the overall operational complexity and number of memory accesses required in Table 1.

For given values of L,  $\ell$ , and N, the value of dnum that minimizes the total number of modular multiplications and plain multiplications is  $(L+1)\sqrt{8\ell+7\log N+32}$  /( $(\ell+1)\sqrt{\log N+22}$ ). The global memory access count is minimized when dnum =  $((L+1)\sqrt{\log N})/((\ell+1)\sqrt{\log N+14})$ . Prior work [HK20] chooses dnum that minimizes the number of ModMuls. However, this could be sub-optimal if an FHE operation is mostly bottlenecked by the global memory bandwidth, which is especially true in GPUs compared to CPUs. Figure 2(a) shows the HMULT time with various dnum values on our baseline CKKS implementation, both with CPUs and GPUs. As stated above, because modern server-class CPUs have a last-level cache of several dozens of megabytes that can accommodate one or two polynomials in FHE operations, the last-level cache absorbs

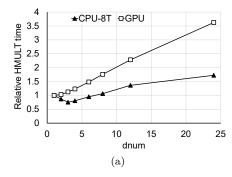

**Figure 2:** (a) HMULT time with 8-threaded CPU (CPU-8T) and our baseline GPU implementation when (N, L) = (65536, 24). (b) A roofline model of multiplication in CKKS with our baseline GPU implementation when  $(N, L, dnum) = (2^{16}, 45, 45)$ . The number of integer instructions is measured with NVIDIA Nsight compute [NVI20].

most of the DRAM traffic. This makes the execution time of HMULT directly proportional to the number of arithmetic operations. In contrast, GPUs have smaller caches and the execution time is for this reason determined instead by the global memory accesses, becoming susceptible to the memory bandwidth and making it preferable to use a smaller dnum for fewer memory accesses.

#### 4.2 Memory-bandwidth Bottleneck of FHE Operations on GPUs

A single ModMul operation is translated into different instructions depending on the type of machine. To understand the actual operational characteristics of HMULT on GPUs, we provide a roofline plot [HP17] of CKKS multiplication in our baseline GPU implementation in Figure 2(b). We measured the integer operation throughput and DRAM access counts using a profiling tool provided by NVIDIA Nsight Compute [NVI20].

Most operations in HMULT are not compute-bound but are instead global-memory-bandwidth bound. Among these operations, Inner-product has the lowest operation intensity, severely bounded by the global memory bandwidth. The operational intensity of Inner-product is even lower than that of the addition operations because the baseline Inner-product implementation accumulates the *i*-th product  $d_2^{(i)} \cdot \mathbf{evk}_i$  into accum (lines 4-7 in Algorithm 10), whose elements are 128 bits (quad-word) long, incurring numerous memory accesses.

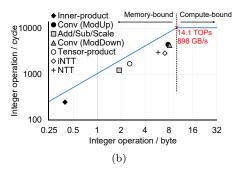

We observe that Inner-product in key-switching is a major bottleneck when attempting to accelerate HMULT because it has an extremely low operational intensity despite its large number of memory accesses, especially with a large dnum. Figure 3 presents the execution time, global memory (DRAM) bandwidth, and instruction throughput (SM utilization) of HMULT with our baseline GPU implementation. For most functions, these DRAM bandwidth utilization rates are higher than those of SM utilization, in good agreement with the low operational intensity shown in the roofline plot (Figure 2)(b). Also, although NTT performs most of the modular multiplications required in HMULT, Inner-product dominates by 54.5% the overall execution time. Because Inner-product is the most memory-intensive operation in HMULT, it utilizes SM in GPU at only 3.4%. The second-most time-consuming function, NTT, also exhibits high global memory utilization (71.0%) and low SM utilization (38.4%) rates.

One of the factors contributing to the large number of memory accesses in Inner-product is the use of a large dnum, as the sizes of the evaluation keys are proportional to dnum  $(\{swk_i\}_{0 \le i < dnum})$ . Throughout this paper, we adopt the generalized key switching strategy in [HK20], which prefers the use of smaller dnum values, reducing the sizes of the keys and thus amortizing the global memory bandwidth bottleneck of Inner-product when run on a GPU. Moreover, we apply memory-centric optimizations that are commonly applicable

**Figure 3:** Execution time, DRAM utilization, and SM utilization of a single FHE-mult on our baseline GPU implementation of CKKS with  $(N, L, dnum) = (2^{16}, 45, 45)$ .

to GPUs, such as operation fusion (kernel fusion [QRHT19]) in both an intra- and an inter-FHE manner, which significantly reduces the bandwidth requirement.

### 5 Memory-centric optimizations for FHE on GPUs

Kernel fusion is a technique that fuses multiple GPU kernels into one kernel. Typical GPU kernels operate in three steps: they load the input data from DRAM into shared memory or registers, compute the data, and store the output data. Kernel fusion combines multiple kernels, and by reusing data in the register file or shared memory, this strategy reduces the number of global memory accesses between kernels. By judiciously applying various kernel fusion methods both in an intra- and inter-FHE-operation manner, we significantly reduce the number of memory accesses required for memory-intensive FHE operations.

#### 5.1 Intra-FHE-operation Fusion

There are a number of opportunities for kernel fusion inside a single FHE operation. More specifically, we show that the major FHE operations in CKKS such as multiplication, rotation, and rescaling have ample opportunities to adopting kernel fusion to reduce the number of memory accesses. Below, we describe how we exploit the kernel fusion technique to those FHE operations.

Fusing the scaling kernel in ModUp with batched iNTT: We suggest and apply two optimizations to ModUp. First, we batch  $\beta$  iNTT kernels in ModUps that are invoked  $\beta$  times per KeySwitch. Each execution of the fast basis conversion in ModUp follows iNTT( $[a]_{C_i'}$ ), as described in Subsection 2.3. When dnum is large enough, the input size of each iNTT  $(LN/\text{dnum} = \alpha N)$  decreases; one cannot maximally exploit thread-level parallelism in GPUs because the throughput of an iNTT kernel decreases due to the kernel call overhead [BVMA18, KJPA20]. Instead of launching numerous small iNTT kernels, we fuse them into a single, large iNTT kernel that takes  $(\alpha\beta)N$  input residues, and launch the large kernel once.

Second, we fuse the scaling kernel of Conv in ModUp (which multiplies either  $[\hat{Q}_j^{''-1}]_{q_j}$  or  $[\hat{Q}_j^{'''-1}]_{p_j}$ ; see Subsection 2.3), with the preceding batched iNTT kernel. Because the scaling kernel has low arithmetic intensity and becomes memory-bound, fusing it with its preceding batched iNTT kernel removes most of the required memory accesses. Specifically, because we perform 8 per-thread iNTT for the batched iNTT kernel, each thread holds eight double-word output elements in its registers, before storing them into the global memory. We multiply each of the eight output elements with its corresponding  $[\hat{Q}_j^{''-1}]_{q_j}$  or  $[\hat{Q}_j^{'''-1}]_{p_j}$ , right before storing them into global memory. This eliminates  $2\alpha\beta N$  memory accesses in total.

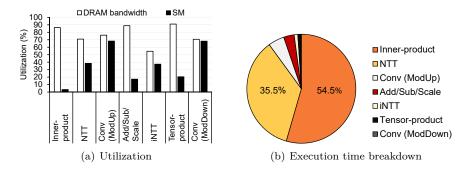

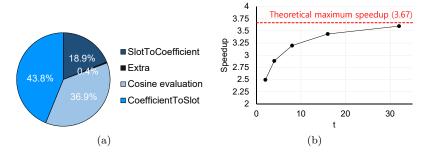

**Figure 4:** (a) Execution time breakdown of a single run of bootstrapping on GPU, (b) speedup of line 9-13 in Algorithm 11 with batching plaintext-ciphertext MAC for various t. The red line represents the maximum speedup, 11/3.  $(N, L, \text{dnum}) = (2^{17}, 29, 3)$ .

Fusing Inner-product in key-switching: Inner-product in key-switching (see Algorithm 10) requires  $(11\beta-4)(\alpha\beta+k)N$  memory accesses in total (see Table 1). Most required global memory accesses come from reading and writing **accum** multiple times. Because each element of **accum** is 128 bits long, these operations account for most of the memory accesses.

To reduce the number of memory accesses, we fuse the three types of kernels in Algorithm 10, which are described in Subsection 3.1, into a single kernel that performs all of the multiplication, mult-and-add, and reduction operations. In the fused kernel, each thread holds the partial sum in its registers until the last mult-and-add operation is complete. This simple but effective approach reduces the number of total memory accesses required from  $(11\beta - 4)(\alpha\beta + k)N$  to  $(3\beta + 2)(\alpha\beta + k)N$ .

Fusing element-wise operations in ModDown with NTT: We fuse two element-wise operations in ModDown, subtraction and scaling with  $[\hat{Q}^{-1}]_{q_j}$  for each j (lines 6-8 in Algorithm 4), with a preceding NTT (line 5). Prior to the fusion step, we call one kernel for subtraction and one for scaling. Similar to the kernel fusion we apply to ModUp, these two operations are applied immediately before storing the NTT's output into global memory, removing  $2(\ell+1)N$  global memory accesses during the subtraction and  $2(\ell+1)N$  during the scaling steps overall.

This fusion strategy in ModDown is also applicable to the rescaling operation, as RESCALE can be understood as ModDown that drops a prime (i.e., ModDown $_{\mathcal{C}_{\ell} \to \mathcal{C}_{\ell-1}}$ ) on both instances of input  $([a]_{\mathcal{C}_{\ell}}, [b]_{\mathcal{C}_{\ell}}) \leftarrow \mathbf{ct}$ . Therefore, we also apply this fusion step when rescaling and evaluate its performance after fusion in Section 6.

#### 5.2 Inter-FHE-operation Fusion

Most of the bootstrapping time is spent evaluating linear transformation. Therefore, we suggest optimizations applicable to linear transformation, i.e., batching plaintext-ciphertext multiply-accumulate (MAC) operations.

Breakdown on bootstrapping: Figure 4(a) shows the execution time breakdown of bootstrapping with one of the representative parameter sets in Section 6, after applying all intra-FHE-operation fusion steps in the previous section. Approximately 62.7% of the bootstrapping time is spent evaluating linear transforms, SlotToCoefficient and Coefficient-ToSlot, which are respectively homomorphic decoding and encoding processes. We focus on these two functions and accelerate their core algorithm, BSGS (see Equation 1).

Batching plaintext-ciphertext multiply-accumulate (MAC): As described in Subsection 2.5, the core operation of SlotToCoefficient and CoefficientToSlot is a series of multiplications between block-diagonal sparse matrices, whose diagonals are encoded into plaintexts, and a vector, which is a ciphertext, using the BSGS algorithm (Equation 1).

Our key observation is that the inner-most sum of BSGS (lines 10-13 in Algorithm 11) exhibits a severe memory bandwidth bottleneck on a GPU, similar to Inner-product (lines

5-7 in Algorithm 10). For a given ciphertext of level  $\ell$ , the number of required memory accesses of the innermost sum of Algorithm 11 is  $5t(\ell+1)N$  for t CMULT and  $6(t-1)(\ell+1)N$  for t-1 HADD. We fuse the kernels for CMULT and HADD in lines 9-13 of Algorithm 11 into a single kernel, reducing the total memory accesses of  $(11t-6)(\ell+1)N$  to  $(3t-1)(\ell+1)N$ . We refer to this fusion as  $batching\ plaintext-ciphertext\ MAC$ .

As CMULT and HADD in Algorithm 11 are memory-bound, the reduction of the number of memory accesses is translated into a speedup of as many as asymptotically 11/3 times with batching plaintext-ciphertext MAC. We benchmark the speedup of line 9-13 in Algorithm 11 with our GPU implementation for various values of t in Figure 4(b). Even with t=2, we obtain a  $2.66\times$  speedup. On the other hand, the overall execution time of BSGS is as follows. Let  $f_{speedup}(t)=(11t-6)/(3t-1)$ . Then, the execution time of Algorithm 11 becomes (l+t-2) (HROTATE time) +  $\{l\cdot t$  (CMULT time) + (t-1)(l-1) (HADD time) $\}/f_{speedup}(t)$ .

We can model the speedup of each execution of BSGS in CoefficientToSlot and SlotTo-Coefficient. For a given radix r, because each block-diagonal sparse matrix (except for the first one, which is initially multiplied with the input first) has 2r-1 diagonals, we should select proper values of l and t in Equation 1 such that  $l \cdot t > 2r-1$ , with both l and t near  $\sqrt{2r-1}$ . Following [HHC19], we select a proper radix r first. For  $N=2^{16}$ , we set r to  $2^5$ , resulting in three matrix-vector multiplications, each with radix  $2^5$  (because  $N/2=(2^5)^3$ ). For  $N=2^{17}$ , as  $\log r=5$  does not divide  $\log(N/2)$  without a remainder, we perform three matrix-vector multiplications, each with radix  $2^5$ ,  $2^5$ , and  $2^6$ . Thus, we can determine the total time of CoefficientToSlot (the same applies to SlotToCoefficient) when  $N=2^{16}$  as follows: (total time of each baby-step giant-step in SlotToCoefficient) = 14 (HROTATE time) +  $\{64$  (CMULT time) + 49 (HADD time)}  $f_{speedup}(8)$ , where  $f_{speedup}(8)=3.56$ .

#### 6 Evaluation

We present the performance improvement in FHE operations in CKKS with our interand intra-FHE-optimizations, the effect of generalized key-switching, and hoisting  $^2$ . All experiments were performed on a single NVIDIA Tesla V100 [NVI17] GPU with CUDA 11.2 and an Intel Xeon Gold 6234 @3.3GHz CPU with eight cores [Int20]. We also put all the evaluation keys and constants into the global memory for both the CPU and GPU implementations. We used all parameters that meet the stipulation of security bit  $\lambda > 80$ , as calculated from the LWE estimator [APS15]. Our parameter sets used for evaluating the performance of bootstrapping add  $2^{-19}$  mean errors to the input message after bootstrapping; these values are small enough so as not to hinder most applications [HK20, CCS19, HHC19, CHK<sup>+</sup>18].

Performance of individual FHE operations: Table 2 summarizes the latency of the FHE operations on a single-threaded CPU, our GPU implementation, and PrivFT [BHM<sup>+</sup>20], the state-of-the-art implementation of CKKS [CHK<sup>+</sup>19] on a GPU. Because PrivFT is closed-source, we compared the latency of each operation provided by the corresponding paper using the same GPU. Also, we compared the performance on the parameter set with the largest level in [BHM<sup>+</sup>20] considering the practical use of FHE. This parameter set with a large level represents parameter sets suitable for applications that do not require bootstrapping.

First, by applying all of the intra-FHE-operation fusion techniques, our optimized GPU implementation beats the baseline CPU implementation by  $152\times$ ,  $153\times$ ,  $229\times$ , and  $135\times$  in HMULT, HROTATE, RESCALE, and HADD, respectively. Second, compared to PrivFT [BHM $^+$ 20], even without the optimizations, our baseline implementation outperforms PrivFT by  $1.67\times$

<sup>&</sup>lt;sup>2</sup> The GPU implementations of the inter- and intra-FHE-optimizations are available in https://github.com/scale-snu/ckks-gpu-core.

| ilizations,    | and I iiv.          | [        |          | .1.                |                    |                              |               |

|----------------|---------------------|----------|----------|--------------------|--------------------|------------------------------|---------------|

|                | Execution time (ms) |          |          |                    |                    |                              | Speedup       |

|                | CPU                 |          | GPU      |                    |                    |                              |               |

|                | 1 thread            | base     |          | $\mathbf{fused}_L$ | $\mathbf{fused}_H$ | PrivFT [BHM <sup>+</sup> 20] |               |

| $\overline{N}$ | $2^{16}$            | $2^{16}$ | $2^{16}$ | $2^{16}$           | $2^{17}$           | $2^{16}$                     |               |

| $\log PQ$      | 2366                | 2366     | 2366     | 2364               | 3220               | 2360*                        |               |

| $\log Q$       | 2305                | 2305     | 2305     | 1693               | 2305               | 2300                         |               |

| ${ m L}$       | 44                  | 44       | 44       | 32                 | 44                 | 44                           |               |

| dnum           | 45                  | 45       | 45       | 3                  | 3                  | 45                           |               |

| $\lambda$      | 98                  | 98       | 98       | 100                | 128                | 98                           |               |

| HMULT          | 2644.8              | 33.51    | 17.4     | 2.96               | 7.96               | 55.884                       | 7.02×         |

| HROTATE        | 2578.9              | 32.93    | 16.83    | 2.55               | 6.6                | -                            | -             |

| RESCALE        | 145.4               | 0.846    | 0.635    | 0.49               | 1.20               | 1.632                        | $1.36 \times$ |

| HADD           | 28.12               | 0.208    | 0.208    | 0.162              | 0.378              | 0.188                        | $0.50 \times$ |

| CMULT          | 26.22               | 0.177    | 0.177    | 0.135              | 0.318              | 0.170                        | $0.54 \times$ |

**Table 2:** Execution time of FHE operations in our single-threaded CPU implementation, GPU implementation without (baseline) and with (**fused**, **fused**<sub>L</sub>, and **fused**<sub>H</sub>) our optimizations, and PrivFT [BHM $^+$ 20].

**Table 3:** Bootstrapping time of our baseline implementation and ones that incrementally adopt MF, IF, and MDF together (Intra-FHE-fusion), batching plaintext-ciphertext MAC (Batching), and hoisting (Hoisting).

| Parameter set                                                   | Execution time (ms) |          |                  |          |          | Speedup (vs. CPU 1 thread) |

|-----------------------------------------------------------------|---------------------|----------|------------------|----------|----------|----------------------------|

| (N, Level, dnum)                                                | CPU                 |          | GPU              |          |          |                            |

| $(logPQ, \lambda)$                                              | 1 thread            | Baseline | Intra-FHE fusion | Batching | Hoisting |                            |

| $ \begin{array}{c} (2^{16}, 34, 5) \\ (2222, 106) \end{array} $ | 79444               | 428.94   | 377.78           | 351.09   | 328.25   | 242×                       |

| $ \begin{array}{c} (2^{17}, 29, 3) \\ (2150, 173) \end{array} $ | 135400              | 719.87   | 623.92           | 568.2    | 526.96   | 257×                       |

in HMULT. Our memory-centric optimizations are effective such that we realize a speedup of  $3.21 \times$  in HMULT (**fused**), compared to that of PrivFT.

We also demonstrated the impact of choosing a proper value of dnum in the GPU implementation. Because using a smaller dnum decreases the multiplicative level with a fixed  $\log PQ$  and security bit, we show two parameter sets having either the same  $\log PQ$  with fewer levels ( $\mathbf{fused}_L$ ), or the same level with higher  $\log PQ$  and N values to ensure high security of 128 bits ( $\mathbf{fused}_H$ ). Comparing the result of  $\mathbf{fused}_H$  with PrivFT, which does not exploit generalized key-switching, we improved the performance by  $7.02\times$  in HMULT. In the  $\mathbf{fused}_H$  case, HADD, RESCALE, and CMULT become slower because the ciphertext size is larger than in  $\mathbf{fused}$ ; however, the execution time of HMULT and HROTATE generally dominates by one order of magnitude. Compared to the method that uses maximum dnum ( $\mathbf{fused}$ ),  $\mathbf{fused}_L$  obtains speedups of  $5.88\times$  and  $6.6\times$  in HMULT and HROTATE, respectively. Our results thus demonstrate the importance of memory-centric optimizations and the proper selection of dnum when accelerating CKKS.

**Performance of bootstrapping:** We evaluate the performance of bootstrapping with our intra- and inter-FHE-operation fusion strategy with hoisting [HS18] in Table 3. For this evaluation, we select two parameter sets with small dnum and moderate levels, which represent bootstrap-friendly parameter sets suited for applications demanding bootstrapping. First, our baseline GPU implementation already provides up to a 185× speedup compared to implementation on a CPU. Using a small dnum value increased the performance gap

<sup>\*</sup> We estimate  $\log P$  as 60 since the paper does not provide the value.

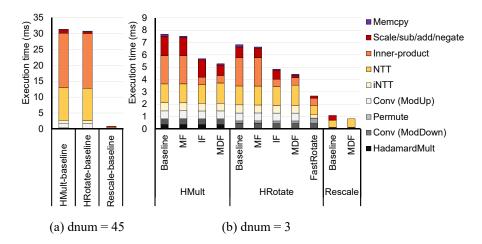

**Figure 5:** Performance of each single FHE operation without fusion (Baseline) and incrementally adopting fusion. FastRotate represents the implementation that applies hoisting after MDF.  $(N, logQ, L) = (2^{16}, 2305, 44)$ .

between the CPU and GPU implementations by relieving the memory bandwidth bottleneck on the GPU. Second, intra-FHE-operation fusions lead to a speedup of up to  $1.15\times$  compared to the Baseline case. Moreover, batching plaintext-ciphertext MAC and hoisting provide an additional speedup of up to  $257\times$  in total compared to the single-thread CPU implementation. In both parameter sets, we found similar speedups on each optimization. **Speedup breakdown:** Using a small dnum significantly reduces the Inner-product time by a factor of 7.48 and 7.50 in our baseline GPU implementation of HMULT and HROTATE, respectively (see Figure 5(a) and (b)). As the number of memory accesses required by Inner-product is reduced to become proportional to dnum, the portion of the Inner-product time changes from 54.6% (55.8%) when dnum= 45 to 29.8% (33.5%) when dnum= 3 in HMULT (HROTATE).

After reducing memory accesses using a small dnum value, we analyze the effect of each intra-FHE-operation fusion (Figure 5(b)). We refer to the three intra-FHE-operation fusions listed in Subsection 5.1 as ModUp Fusion (MF), Inner-product Fusion (IF), and ModDown Fusion (MDF). Figure 5(b) shows the execution time breakdown when we applied MF, IF, and MDF incrementally. MF increases the overall performance of HMULT and HROTATE by  $1.02\times$  and  $1.03\times$ , respectively. The speedup is relatively small, as the size of iNTT in ModUp is small, taking up a small portion in the overall execution time. On top of MF, IF significantly decreases the execution time of Inner-product by reducing the number of memory accesses by up to a factor of 11/3, resulting in a  $3.75\times(3.75\times)$  speedup in Inner-product and a  $1.35\times(1.41\times)$  speedup in total for HMULT (HROTATE). Lastly, MDF increases the overall performance by  $1.46\times$ ,  $1.54\times$ , and  $1.32\times$  correspondingly for HMULT, HROTATE, and RESCALE compared to the baseline.

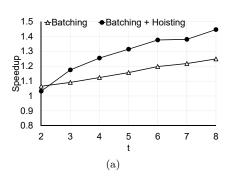

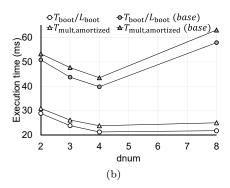

We also evaluate the effectiveness of hoisting [HS18] in HROTATE, shown as a distinct column in Figure 5(b). With hoisting, FastRotate outperforms HROTATE with MDF by  $1.65\times$ , as it does not require ModUp or multiple NTT/iNTT executions. The execution time for permutation (Frobenius map in the NTT domain) increases by  $2.32\times$  as the size of the permutation becomes larger by precomputing ModUp; however, the performance benefit outweighs the cost as permutation only accounted for 4% in HROTATE with MDF. Performance of Baby-step Giant-step: Figure 6(a) shows the performance improvement in BSGS with batching plaintext-ciphertext MAC and hoisting with various values of t. Batching plaintext-ciphertext MAC improves the performance up to  $1.25\times$ . Moreover, applying hoisting results in a speedup of up to  $1.45\times$ , while providing no benefit when t=2 as we perform only one FastRotate and thus cannot save any ModUp.

**Figure 6:** (a) Speedup of evaluation of BSGS (Algorithm 11) with batching plaintext-ciphertext MAC (Batching) and hoisting over t. (b) Amortized FHE-mult time ( $T_{\text{mult,Amortized}}$ ) for a given  $\log PQ \approx 2450$  and N =  $2^{16}$  (97-bit security).

Amortized FHE-mult time: We propose a new metric for performance that reflects the performance of actual applications requiring bootstrapping: amortized FHE-mult time. It considers both the bootstrapping cost and the number of multiplications between two consecutive bootstrapping operations. Let one perform consecutive HMULT until the level of a ciphertext is depleted, perform bootstrapping, and then repeat this process. We define the amortized FHE-mult time as  $T_{\rm mult,amortized} = T_{\rm mult} + \frac{T_{\rm boot}}{L_{\rm boot}}$ , where  $T_{\rm mult}$  is the average time of HMULT between two bootstrapping operations,  $T_{\rm boot}$  is the bootstrapping time, and  $L_{\rm boot}$  is the number of HMULT operations between bootstrappings.

Figure 6(b) shows the amortized FHE-mult time of our best-performing and baseline GPU implementation with various values of dnum for a given security bit. In both implementations, the amortized time becomes minimal when  $\mathtt{dnum} = 4$  (24.35 ms and 43.5 ms for the optimized and baseline cases, respectively). However, our optimized implementation greatly reduces the performance gap between the optimal dnum and the large value ( $\mathtt{dnum} = 8$ ), as it significantly amortizes the memory bandwidth pressure by applying memory-centric optimizations. This makes high dnum values more attractive for those who want more security with the parameter sets that consider bootstrapping.

Our optimized implementation of CKKS outperforms the baseline by  $1.68 \times$ ,  $1.78 \times$ ,  $1.79 \times$ , and  $2.46 \times$  with dnum values of 2, 3, 4, and 8, respectively. By adopting generalized key-switching as well as memory-centric optimizations, the amortized FHE-mult time of our optimized GPU implementation even outperforms the single multiplication time of PrivFT [BHM $^+$ 20], which does not support bootstrapping.